5.2. 冯·诺依曼架构

冯·诺依曼架构是大多数现代计算机的基础。在本节中,我们将简要介绍该架构的主要组件。

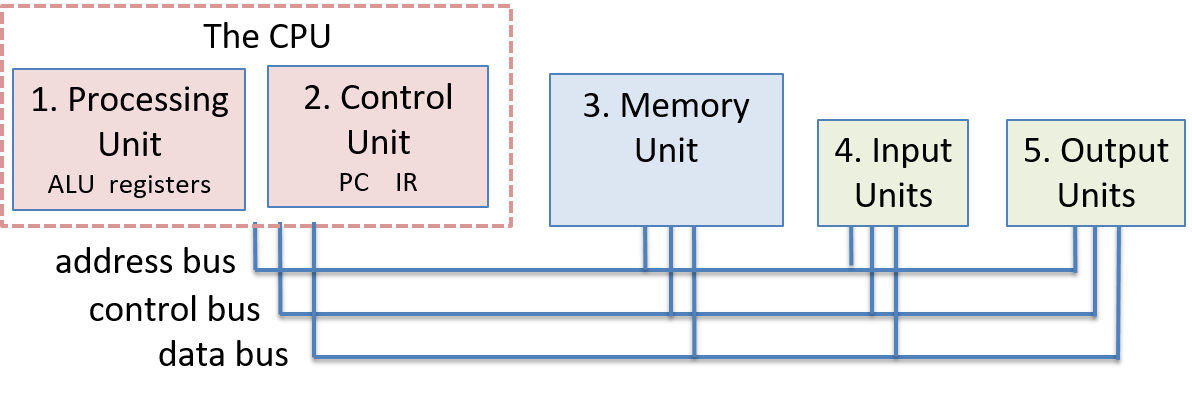

冯·诺依曼架构(如图 1 所示)由五个主要部分组成:

- 处理单元执行程序指令。

- 控制单元驱动处理单元上的程序指令执行。处理单元和控制单元共同构成了 CPU。

- 内存单元存储程序数据和指令。

- 输入单元在计算机上加载程序数据和指令并启动程序执行。

- 输出单元存储或接收程序结果。

总线连接各个单元,并被单元用来相互发送控制和数据信息。总线是一种在通信端点(值的发送者和接收者)之间传输二进制值的通信通道。例如,连线接内存单元和 CPU 的数据总线可以实现为 32 条并行,它们一起传输 4 字节值,每条线上传输 1 位。通常,体系结构具有单独的总线用于在单元之间发送数据、内存地址和控制。单元使用控制总线发送控制信号来请求或通知其他单元采取行动,使用地址总线将读写请求的内存地址发送到内存单元,使用数据总线在单元之间传输数据。

图 1. 冯·诺依曼架构由处理、控制、内存、输入和输出单元组成。控制和处理单元组成 CPU,其中包含 ALU、通用 CPU 寄存器和一些专用寄存器(IR 和 PC)。这些单元通过总线连接,用于单元之间的数据传输和通信。

图 1. 冯·诺依曼架构由处理、控制、内存、输入和输出单元组成。控制和处理单元组成 CPU,其中包含 ALU、通用 CPU 寄存器和一些专用寄存器(IR 和 PC)。这些单元通过总线连接,用于单元之间的数据传输和通信。

5.2.1. CPU

控制和处理单元共同实现 CPU,它是计算机中对程序数据执行程序指令的部分。

5.2.2. 处理单元

冯·诺依曼机的处理单元由两部分组成。第一部分是算术/逻辑单元(ALU),它执行数学运算,例如加法、减法和逻辑或等等。现代 ALU 通常执行大量算术运算。处理单元的第二部分是一组寄存器。寄存器是一个小型、快速的存储单元,用于保存程序数据和 ALU 正在执行的指令。至关重要的是,在冯·诺依曼架构中没有指令和数据之间的区别。无论出于何种意图和目的,指令都是数据。因此每个寄存器能够保存一个数据字。

5.2.3. 控制单元

控制单元通过从内存加载程序指令并将指令操作数和操作输入到处理单元来驱动程序指令的执行。控制单元还包括一些存储器,用于跟踪执行状态并确定下一步要采取的操作:程序计数器 (PC) 保存下一条要执行的指令的内存地址,指令寄存器 (IR) 存储从内存加载的当前正在执行的指令。

5.2.4. 内存单元

内存是冯·诺依曼架构的一项关键创新。它提供靠近处理单元的程序数据存储,大大减少了执行计算的时间。内存单元存储程序数据和程序指令——存储程序指令是冯·诺依曼架构存储程序模型的关键部分。

内存大小因系统而异。但是,系统的 ISA 限制了它可以表达的地址范围。在现代系统中,内存的最小可寻址单位是 1 个字节(8 位),因此每个地址对应于一个字节存储的唯一内存位置。因此,32 位架构通常支持的最大地址空间大小为 232,这对应于 4 千兆字节 (GiB) 的可寻址内存。

术语 内存 有时指系统中的整个存储层次结构。它可以包括处理单元中的寄存器以及硬盘驱动器 (HDD) 或固态驱动器 (SSD) 等辅助存储设备。在 存储和内存层次结构章节 中,我们详细讨论了内存层次结构。现在,我们将术语“内存”与内部 随机存取存储器 (RAM) 互换使用——可由中央处理单元访问的内存。RAM 存储是随机访问的,因为所有 RAM 存储位置(地址)都可以直接访问。将 RAM 视为地址的线性数组很有用,其中每个地址对应一个字节的内存。

历史上的字(word)大小

字长 由 ISA 定义,是处理器作为单个单元处理的标准数据大小的位数。标准字长多年来一直在波动。对于 EDVAC,建议字长为 30 位。在 20 世纪 50 年代,36 位字长很常见。随着 20 世纪 60 年代 IBM 360 的创新,字长或多或少变得标准化,并开始从 16 位扩展到 32 位,再到今天的 64 位。如果您更详细地研究英特尔架构,您可能会注意到其中一些旧决策的残余,因为 32 位和 64 位架构是作为原始 16 位架构的扩展而添加的。

5.2.5. 输入和输出 (I/O) 单元

控制、处理和存储单元构成了计算机的基础,而输入和输出单元则使计算机能够与外界交互。具体来说,它们提供了将程序的指令和数据加载到内存中、将其数据存储在内存之外以及将其结果显示给用户的机制。

输入单元由一组设备组成,这些设备使用户或程序能够将数据从外部世界传输到计算机中。当今最常见的输入设备是键盘和鼠标。其他例子包括摄像头和麦克风。

输出单元由一组设备组成,这些设备将计算机的计算结果传回外部世界或将结果存储在内部存储器之外。例如,显示器是一种常见的输出设备。其他输出设备包括扬声器和触觉设备。

一些现代设备,例如触摸屏,既可用作输入,又可用作输出,使用户能够从单个统一的设备输入和接收数据。

固态硬盘和硬盘是另一种既可用作输入设备又可用作输出设备的设备。这些存储设备在存储操作系统加载到计算机内存中运行的程序可执行文件时充当输入设备,在存储写入程序结果的文件时充当输出设备。

5.2.6. 冯·诺依曼机器实例:执行程序

组成冯·诺依曼体系结构的五个单元协同工作,实现获取-解码-执行-存储操作循环,共同执行程序指令。此循环从程序的第一条指令开始,并重复进行,直到程序退出:

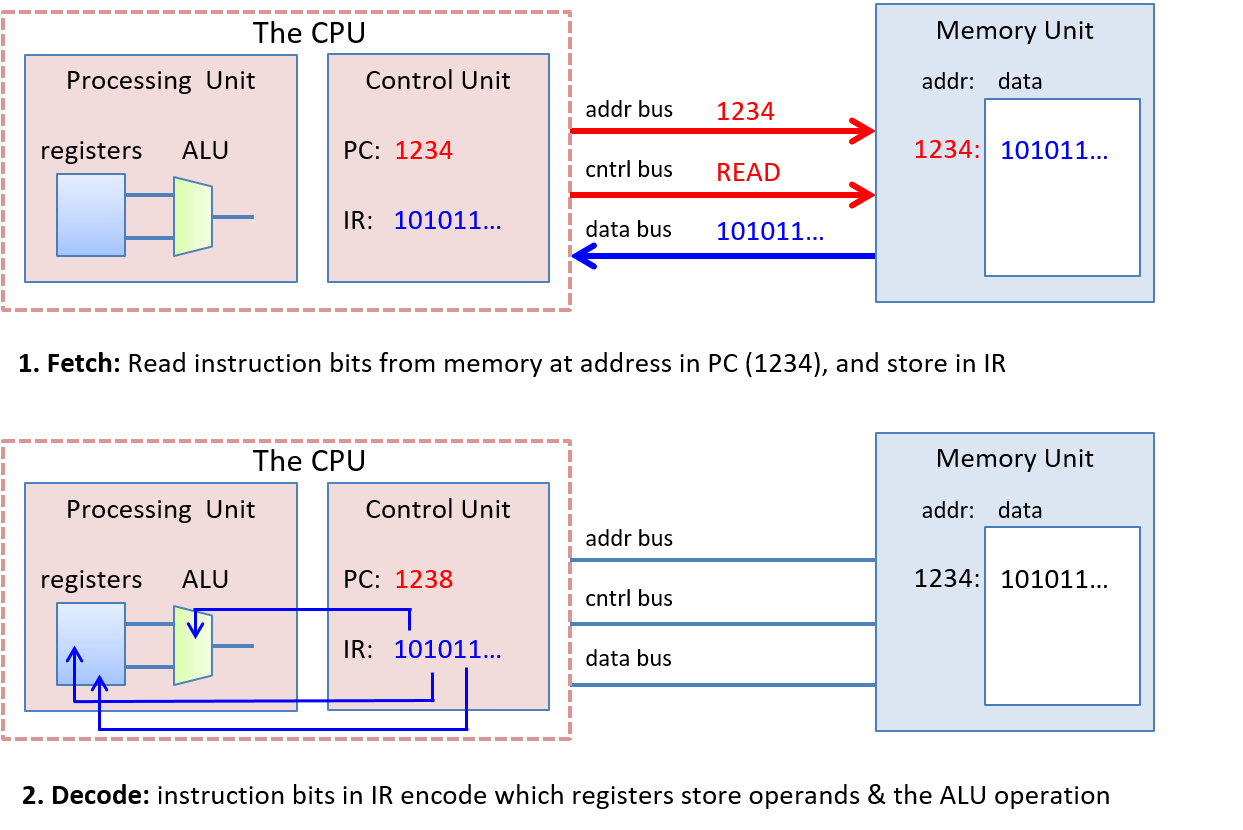

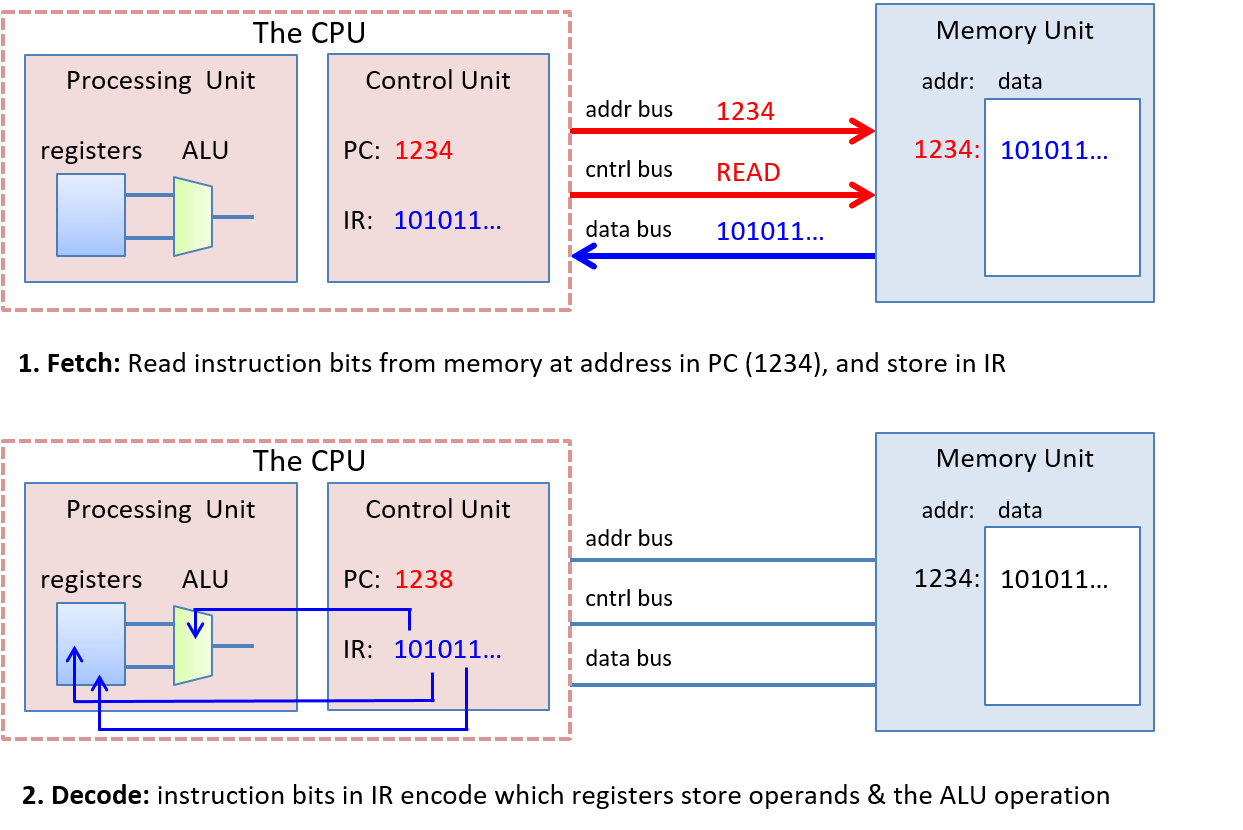

- 控制单元从内存中_获取_下一条指令。控制单元有一个特殊的寄存器,即程序计数器 (PC),其中包含下一条要获取的指令的地址。它将该地址放在_地址总线_上,并将_读取_命令放在_控制总线_上发送到内存单元。然后,内存单元读取存储在指定地址的字节,并通过_数据总线_将它们发送到控制单元。指令寄存器 (IR) 存储从内存单元接收到的指令的字节。控制单元还增加 PC 的值以存储新的下一条要获取的指令的地址。

- 控制单元对存储在 IR** 中的指令进行解码。它对编码要执行的操作的指令位和编码操作数所在位置的位进行解码。指令位根据 ISA 对其指令编码的定义进行解码。控制单元还从数据操作数值的位置(从 CPU 寄存器、内存或编码在指令位中)获取数据操作数值,作为处理单元的输入。

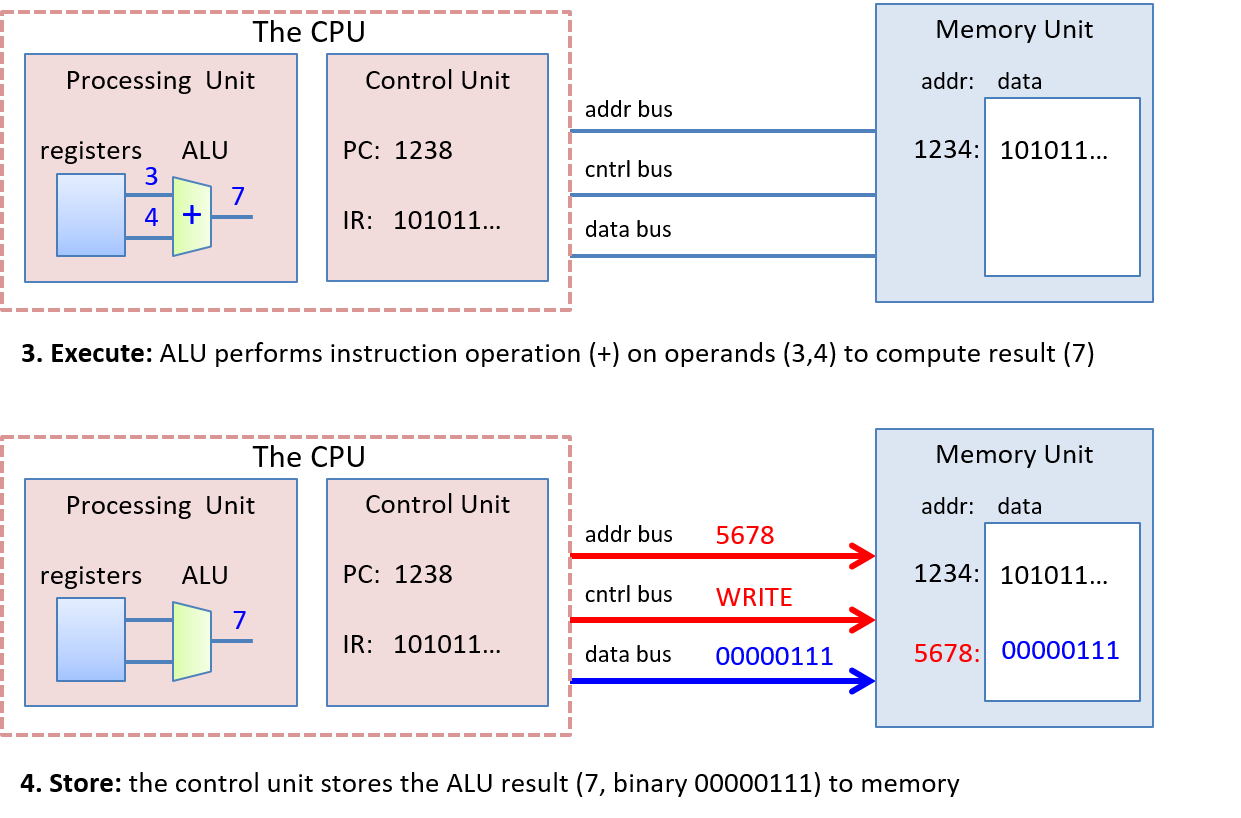

- 处理单元执行指令。ALU 对指令数据操作数执行指令操作。

- 控制单元将结果存储到内存。处理单元执行指令的结果存储到内存中。控制单元通过将结果值放在数据总线上、将存储位置的地址放在地址总线上、将写入命令放在控制总线上,将结果写入内存。内存单元接收到后,将值写入指定地址的内存中。

输入和输出单元不直接参与程序指令的执行。相反,它们通过加载程序指令和数据以及存储或显示程序计算的结果来参与程序的执行。

图2 和 图3 显示了冯·诺依曼架构执行加法指令的四个阶段,该指令的操作数存储在 CPU 寄存器中。在提取阶段,控制单元读取存储在 PC (1234) 中的内存地址处的指令。它在地址总线上发送地址,在控制总线上发送 READ 命令。内存单元接收请求,读取地址 1234 处的值,并将其发送到数据总线上的控制单元。控制单元将指令字节放入 IR 寄存器中,并使用下一条指令的地址(此示例中为 1238)更新 PC。在解码阶段,控制单元将指令中指定要执行哪种操作的位馈送到处理单元的 ALU,并使用指定哪些寄存器存储操作数的指令位将操作数值从处理单元的寄存器读入 ALU(此示例中的操作数值为 3 和 4)。在执行阶段,处理单元的 ALU 部分对操作数执行运算以产生结果(3 + 4 等于 7)。最后,在存储阶段,控制单元将结果(7)从处理单元写入内存单元。内存地址(5678)在地址总线上发送,WRITE 命令在控制总线上发送,要存储的数据值(7)在数据总线上发送。内存单元接收此请求并将 7 存储在内存地址 5678 处。在此示例中,我们假设存储结果的内存地址已编码在指令位中。

图 2. 冯·诺依曼架构执行的提取和解码阶段,用于示例加法指令。操作数、结果和内存地址显示为十进制值,内存内容显示为二进制值。 ^0fe5cb

图 3. 冯·诺依曼架构的执行和存储阶段是示例加法指令。操作数、结果和内存地址显示为十进制值,内存内容显示为二进制值。 ^18b4b3